Sony DRAM Laminated 3-layer image CMOS sensor

ソニーは、業界で初めてスマートフォン向けとなる DRAM を積層した3層構造の積層型 CMOS イメージセンサーを開発。高速読み出しにより、フォーカルプレーン歪みを抑えた静止画やスーパースローモーション動画を撮影可能に。

■ 仕様

■ 3層構造 CMOS イメージセンサー

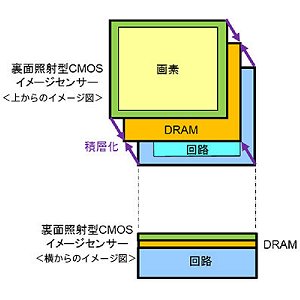

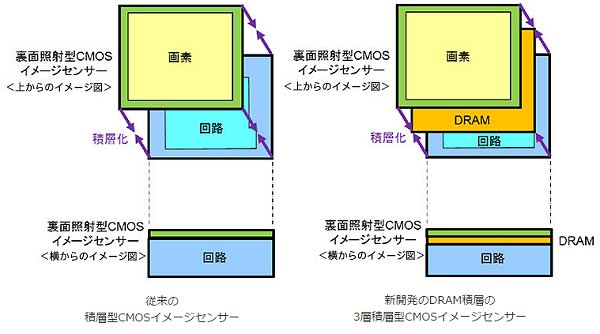

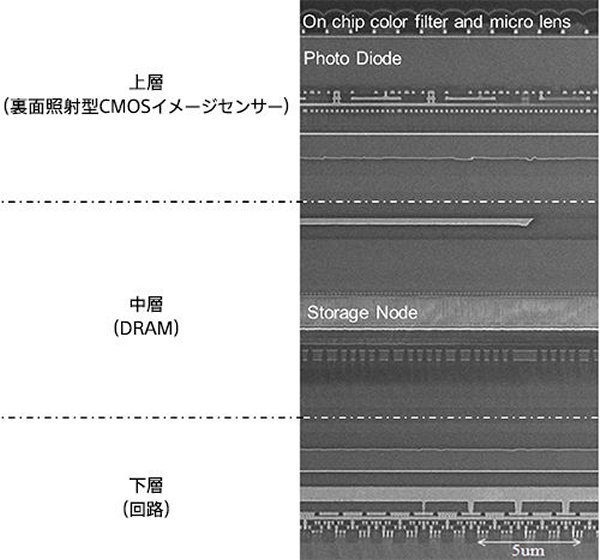

業界初となる DRAM を積層した3層構造の積層型CMOSイメージセンサー。従来の裏面照射型画素部分と信号処理回路部分との2層構造の積層型CMOSイメージセンサーに、さらにDRAMを積層したものです。3層にそれぞれ搭載された回路間のノイズの低減など、設計上の技術的な課題を克服しています。また、ソニーが業界に先駆け長年培ってきた積層型の製造技術や知見などを活用することで、3層化で構造が複雑になっても、高い品質と信頼性を実現しています。

■ 開発品の主な特長

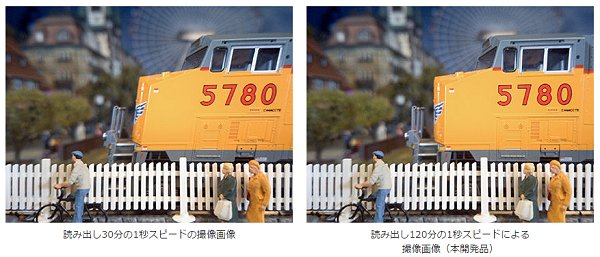

高速で低消費電力の特性を持つ大容量 DRAM を積層し、1930万画素サイズの静止画1枚を120分の1秒(従来比約4倍)で読み出すことができる高速読み出しを実現することで、画素の行毎の読み出し時間のずれを抑えることができます。これにより、露光時間を制御するメカニカルシャッターの無いスマートフォンでも、動きの速い被写体の撮影時に起こりやすいフォーカルプレーン歪みを抑えた静止画の撮影が可能となります。

■ スローモーション動画

高速読み出しを可能にしたことにより、フルHD(1920×1080画素)サイズで毎秒最大1,000フレーム(従来比約8倍)のスーパースローモーション動画の撮影が可能です。通常速度の撮影データと、DRAM に蓄積した毎秒最大1,000フレームの高速撮影データとを本イメージセンサーから出力し、外付けの ISP (画像処理回路)で信号処理することで、通常速度の動画とスーパースローモーション動画を、シームレスに繋いだ躍動感のある動画作品をスマートフォンで撮影することができます。

ニュースリリース – ソニー

http://www.sony.co.jp/SonyInfo/News/Press/201702/17-013/

名前 (Name) が空欄だと「匿名」になり、コメント反映に時間がかかります。名前を入れると投稿後もコメントの編集や削除が可能です。Email は入力しても表示されません。コメントは1度の投稿で【300文字】までとなります。

13:51

CMOSセンサーの致命的な弱点であったローリングシャッター現象が防げるようになるのが一番の利点でしょうか?

でもいくらXperiaではプレミアムおまかせオートで800万画素にシュリンクさせて撮影出来るからといって、他社にも供給するんですし出来れば画素数はもう少し抑えてもらいたかったです。